Inter-Integrated Circuit Bus (I2C): Unterschied zwischen den Versionen

Die Seite wurde neu angelegt: „Kategorie:Arduino '''Autor:''' Prof. Dr.-Ing. Schneider“ |

|||

| (15 dazwischenliegende Versionen desselben Benutzers werden nicht angezeigt) | |||

| Zeile 1: | Zeile 1: | ||

[[Kategorie:Arduino]] | [[Kategorie:Arduino]] | ||

'''Autor:''' [[Benutzer:Ulrich_Schneider| Prof. Dr.-Ing. Schneider]] | '''Autor:''' [[Benutzer:Ulrich_Schneider| Prof. Dr.-Ing. Schneider]] | ||

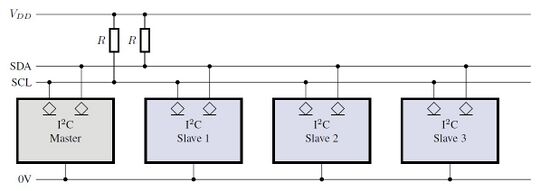

[[Datei:Bussystem-I2C.jpg|thumb|rigth|550px|Abb. 1: Bussystem I<sup>2</sup>C]] | |||

== Einleitung == | |||

Zu den seriellen Bussen zählt der '''Inter-Integrated Circuit''' Bus, kurz I<sup>2</sup>C-Bus (gesprochen „IQuadrat-C“). Ursprünglich wurde der Bus in den 80er Jahren von Philips Semiconductors für die Verbindung von Komponenten der Unterhaltungselektronik entwickelt. Heute kommt er in vielen Computerkomponenten zum Einsatz, vom PC bis zu eingebetteten Systemen. Für die kollisionsfreie Kommunikation mit anderen I<sup>2</sup>C Komponenten werden eindeutige Adressen benötigt, welche von NXP-Semiconductor2 bezogen werden können. | |||

Die Kommunikation auf dem bidirektionalen Bus erfolgt über eine Takt- (<code>SCL</code>: serial clock) und eine Datenleitung (<code>SDA</code>: serial data), deren Pegel sich auf eine gemeinsame Masse beziehen. | |||

Die Busteilnehmer besitzen Open-Drain- bzw. Open-Kollektor-Ausgänge, die auf dem Bus mit Pull-Up-Widerständen gegen die Betriebsspannung <code>VDD</code> geschaltet werden (vgl. Abb. 1). | |||

== Pegel == | |||

{| class="wikitable" | |||

|- | |||

| Low-Pegel || <math>U < 0,3\cdot V_{DD}</math> | |||

|- | |||

| High-Pegel || <math>U > 0,7\cdot V_{DD}</math> | |||

|- | |||

|} | |||

== Geschwindigkeit == | |||

Auf dem Bus ist die bidirektionale Kommunikation mit Busgeschwindigkeiten von | |||

* 100 kbit/s im Standard-Mode, | |||

* über 400 kbit/s im Fast-Mode, | |||

* bis zu 1 Mbit/s im Fast-Mode Plus (FM+) | |||

* und 3,4 Mbit/s im High-Speed Mode | |||

möglich. Darüber hinaus existiert ein unidirektionaler Ultra Fast-Mode mit einer Datenrate von bis zu 5 Mbit/s. | |||

== Multi-Master-Architektur == | |||

Der Bus ist Multi-Master fähig. Üblicherweise handelt es sich bei einem Master um einen Mikrocontroller, welcher mit der angeschlossenen Peripherie über den Bus kommuniziert. Wenn mehrere Controller den gleichen Bus bedienen oder über den Bus miteinander kommunizieren, | |||

arbeitet ein Controller als Master und der andere als Slave. Vom jeweils aktuellen Master wird das Taktsignal generiert. Eine Bus-Arbitration Prozedur sorgt bei gleichzeitigem Aktivieren von zwei Master-Geräten für das Erkennen und Behandeln der Kollision. Damit eignet sich | |||

der Bus auch für die Zusammenschaltung mehrerer aktiver Baugruppen, wie z. B. den Aufbau eines Controllernetzwerkes mit mehreren Controllern. Die Datenübertragung, Handshake und Bus Arbitration werden von NXP auf den Ebenen 1 und 2 des OSI-Modells spezifiziert | |||

== Kommunikation == | |||

Die Kommunikation basiert auf einem einfachen Schema. Abgesehen von Steuersignalen werden die Informationen in Form von 8-Bit-Blöcken (Oktetts) übertragen. Ein Oktett beinhaltet | |||

Adressen oder Daten. Dazu erhält jedes Gerät vom Hersteller eine eindeutige Adresse der Länge 7 Bit bzw. bei neueren Geräten 10 Bit. Meist umfasst die Adresse nur das Präfix, die letzten | |||

drei Bits können vom Anwender durch Steuerleitungen am I<sup>2</sup>C-Controller konfiguriert werden, was die Nutzung von mehreren gleichartigen Geräten am Bus erlaubt. Gibt es nur einen | |||

Controller als Master, werden heute auch Chip Select (<code>CS</code>) bzw. Chip Enable (<code>CE</code>) Leitungen genutzt, über die der Controller gezielt einen I<sup>2</sup>C-Slave aktiviert. | |||

Zu Beginn der Übertragung erzeugt der Master ein Startsignal mit <code>SCL=1</code> und fallender Flanke | |||

auf SDA. Anschließend legt er die Adresse auf den Bus. Zu jedem Bit wird | |||

vom Master ein Taktimpuls erzeugt. Das Bit auf SDA ist gültig, wenn <code>SCL=1</code> ist. In dieser | |||

Phase darf sich <code>SDA</code> nicht ändern, abgesehen von den Steuersignalen. Nach der 7-Bit-Adresse | |||

wird im ersten Block das R/W-Bit übertragen, welches die anschließende Kommunikationsrichtung, Lesen oder Schreiben zum Slave festlegt. Nach jedem Oktett wird als 9. Bit ein Bestätigungssignal | |||

vom jeweiligen Empfänger gesendet. Wenn der Master etwas an einen Slave sendet, werden die ersten 8 Bit vom Master auf <code>SDA</code> gelegt, das 9. Bit vom Slave. Der Empfang war erfolgreich, wenn <code>SDA=0</code> ist. Dies wird als <code>ACK</code> für acknowledge bezeichnet, <code>SDA=1</code> als | |||

<code>NACK</code> für not acknowledged. Bei NACK wird die Übertragung vom Master beendet. | |||

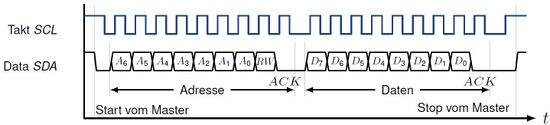

[[Datei:Zeitdiagramm-I2C.jpg|thumb|rigth|550px|Abb. 2: Bussystem I<sup>2</sup>C]] | |||

Nach der Adresse folgt üblicherweise die Nummer des internen Registers, welches gelesen | |||

oder beschrieben werden soll, gefolgt von den Daten in einem oder mehreren Blöcken. Den | |||

Abschluss bildet das vom Master generierte Stop-Signal (<code>SCL=1</code> mit steigender Flanke auf | |||

<code>SDA</code>). Es gibt einige Ausnahmen und Verfahren zur Beschleunigung für fortlaufendes Senden | |||

sowie zur Taktverlängerung, welche hier nicht erläutert werden. | |||

Für den I<sup>2</sup>C-Bus ist ein umfassendes Sortiment an Komponenten verfügbar. Viele Mikrocontroller | |||

besitzen ein I<sup>2</sup>C-Interface und Hardwareunterstützung zur Busansteuerung. Integrierte Sensoren besitzen häufig ein I<sup>2</sup>C-Interface. Zusätzlich | |||

gibt es Bus- und Protokollumsetzer, die eine Kommunikation zwischen I<sup>2</sup>C-Komponenten und | |||

Komponenten an anderen Bussen, z. B. dem SPI-Bus ermöglichen. | |||

Der I<sup>2</sup>C-Bus wird nicht für die Datenübertragung über größere Entfernungen genutzt. Übliche | |||

Verbindungen liegen im Bereich von unter einem Meter. Ein Grund dafür ist die Störanfälligkeit | |||

des Busses bei längeren Leitungen, weshalb man ihn meist nur innerhalb eines geschirmten | |||

Gerätes verwendet. | |||

== Literatur == | |||

# Rost, M; Wefel, S.: ''Sensorik für Informatiker.'' Berlin: de Gruyter, 1. Auflage 2016 | |||

== Video == | |||

{{#ev:youtube|https://www.youtube.com/watch?v=Sc_qkO2tI1M | 250 | | EdisTechlab: I2C in 8 Minuten verstehen! |frame}} | |||

Aktuelle Version vom 26. November 2022, 12:06 Uhr

Autor: Prof. Dr.-Ing. Schneider

Einleitung

Zu den seriellen Bussen zählt der Inter-Integrated Circuit Bus, kurz I2C-Bus (gesprochen „IQuadrat-C“). Ursprünglich wurde der Bus in den 80er Jahren von Philips Semiconductors für die Verbindung von Komponenten der Unterhaltungselektronik entwickelt. Heute kommt er in vielen Computerkomponenten zum Einsatz, vom PC bis zu eingebetteten Systemen. Für die kollisionsfreie Kommunikation mit anderen I2C Komponenten werden eindeutige Adressen benötigt, welche von NXP-Semiconductor2 bezogen werden können.

Die Kommunikation auf dem bidirektionalen Bus erfolgt über eine Takt- (SCL: serial clock) und eine Datenleitung (SDA: serial data), deren Pegel sich auf eine gemeinsame Masse beziehen.

Die Busteilnehmer besitzen Open-Drain- bzw. Open-Kollektor-Ausgänge, die auf dem Bus mit Pull-Up-Widerständen gegen die Betriebsspannung VDD geschaltet werden (vgl. Abb. 1).

Pegel

| Low-Pegel | |

| High-Pegel |

Geschwindigkeit

Auf dem Bus ist die bidirektionale Kommunikation mit Busgeschwindigkeiten von

- 100 kbit/s im Standard-Mode,

- über 400 kbit/s im Fast-Mode,

- bis zu 1 Mbit/s im Fast-Mode Plus (FM+)

- und 3,4 Mbit/s im High-Speed Mode

möglich. Darüber hinaus existiert ein unidirektionaler Ultra Fast-Mode mit einer Datenrate von bis zu 5 Mbit/s.

Multi-Master-Architektur

Der Bus ist Multi-Master fähig. Üblicherweise handelt es sich bei einem Master um einen Mikrocontroller, welcher mit der angeschlossenen Peripherie über den Bus kommuniziert. Wenn mehrere Controller den gleichen Bus bedienen oder über den Bus miteinander kommunizieren, arbeitet ein Controller als Master und der andere als Slave. Vom jeweils aktuellen Master wird das Taktsignal generiert. Eine Bus-Arbitration Prozedur sorgt bei gleichzeitigem Aktivieren von zwei Master-Geräten für das Erkennen und Behandeln der Kollision. Damit eignet sich der Bus auch für die Zusammenschaltung mehrerer aktiver Baugruppen, wie z. B. den Aufbau eines Controllernetzwerkes mit mehreren Controllern. Die Datenübertragung, Handshake und Bus Arbitration werden von NXP auf den Ebenen 1 und 2 des OSI-Modells spezifiziert

Kommunikation

Die Kommunikation basiert auf einem einfachen Schema. Abgesehen von Steuersignalen werden die Informationen in Form von 8-Bit-Blöcken (Oktetts) übertragen. Ein Oktett beinhaltet

Adressen oder Daten. Dazu erhält jedes Gerät vom Hersteller eine eindeutige Adresse der Länge 7 Bit bzw. bei neueren Geräten 10 Bit. Meist umfasst die Adresse nur das Präfix, die letzten

drei Bits können vom Anwender durch Steuerleitungen am I2C-Controller konfiguriert werden, was die Nutzung von mehreren gleichartigen Geräten am Bus erlaubt. Gibt es nur einen

Controller als Master, werden heute auch Chip Select (CS) bzw. Chip Enable (CE) Leitungen genutzt, über die der Controller gezielt einen I2C-Slave aktiviert.

Zu Beginn der Übertragung erzeugt der Master ein Startsignal mit SCL=1 und fallender Flanke

auf SDA. Anschließend legt er die Adresse auf den Bus. Zu jedem Bit wird

vom Master ein Taktimpuls erzeugt. Das Bit auf SDA ist gültig, wenn SCL=1 ist. In dieser

Phase darf sich SDA nicht ändern, abgesehen von den Steuersignalen. Nach der 7-Bit-Adresse

wird im ersten Block das R/W-Bit übertragen, welches die anschließende Kommunikationsrichtung, Lesen oder Schreiben zum Slave festlegt. Nach jedem Oktett wird als 9. Bit ein Bestätigungssignal

vom jeweiligen Empfänger gesendet. Wenn der Master etwas an einen Slave sendet, werden die ersten 8 Bit vom Master auf SDA gelegt, das 9. Bit vom Slave. Der Empfang war erfolgreich, wenn SDA=0 ist. Dies wird als ACK für acknowledge bezeichnet, SDA=1 als

NACK für not acknowledged. Bei NACK wird die Übertragung vom Master beendet.

Nach der Adresse folgt üblicherweise die Nummer des internen Registers, welches gelesen

oder beschrieben werden soll, gefolgt von den Daten in einem oder mehreren Blöcken. Den

Abschluss bildet das vom Master generierte Stop-Signal (SCL=1 mit steigender Flanke auf

SDA). Es gibt einige Ausnahmen und Verfahren zur Beschleunigung für fortlaufendes Senden

sowie zur Taktverlängerung, welche hier nicht erläutert werden.

Für den I2C-Bus ist ein umfassendes Sortiment an Komponenten verfügbar. Viele Mikrocontroller besitzen ein I2C-Interface und Hardwareunterstützung zur Busansteuerung. Integrierte Sensoren besitzen häufig ein I2C-Interface. Zusätzlich gibt es Bus- und Protokollumsetzer, die eine Kommunikation zwischen I2C-Komponenten und Komponenten an anderen Bussen, z. B. dem SPI-Bus ermöglichen.

Der I2C-Bus wird nicht für die Datenübertragung über größere Entfernungen genutzt. Übliche Verbindungen liegen im Bereich von unter einem Meter. Ein Grund dafür ist die Störanfälligkeit des Busses bei längeren Leitungen, weshalb man ihn meist nur innerhalb eines geschirmten Gerätes verwendet.

Literatur

- Rost, M; Wefel, S.: Sensorik für Informatiker. Berlin: de Gruyter, 1. Auflage 2016